# Data Manual

Printed on

ENVIRONMENTALLY FRIENDLY OFFSET

Cover on

ENVIROCOTE 250GSM BOARD

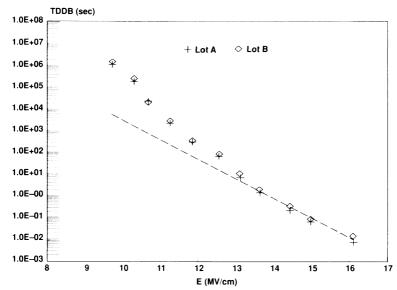

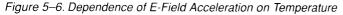

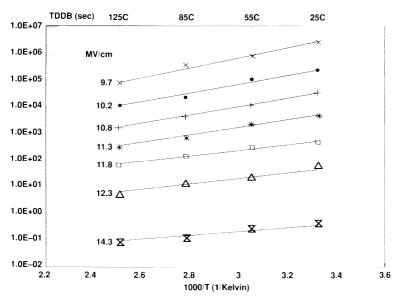

| General Information               | 1 |

|-----------------------------------|---|

| TDO FDOA Ossiles Date             |   |

| TPC FPGA Series Data              | 2 |

| Action Logic System Overview      | 3 |

| FPGA Design Software and Hardware | 4 |

| Quality and Reliability Data      | 5 |

| Applications                      | 6 |

| Ordering Information              | 7 |

# Field Programmable Gate Array Data Manual

#### IMPORTANT NOTICE

Texas Instruments Incorporated (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Please be aware that TI products are not intended for use in life-support appliances, devices, or systems. Use of TI product in such applications requires the written approval of the appropriate TI officer. Certain applications using semiconductor devices may involve potential risks of personal injury, property damage, or loss of life. In order to minimize these risks, adequate design and operating safeguards should be provided by the customer to minimize in the risk of the customer using TI devices or systems.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1993, Texas Instruments Incorporated

#### INTRODUCTION

This data book contains technical information on the Texas Instruments (TI) Field Programmable Gate Array (FPGA) product. This line of products from TI offers designers the ease of use and quick time to market of Programmable Logic Devices, along with performance and high density of gate arrays.

TI FPGAs are based on antifuse technology. The antifuse provides programmability to the device and offers great advantage for high density and performance at low cost.

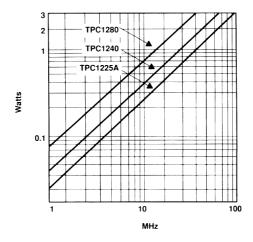

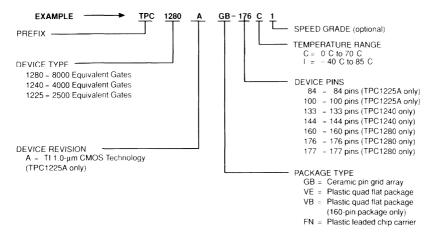

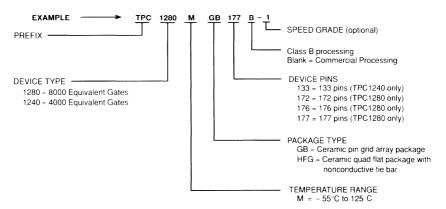

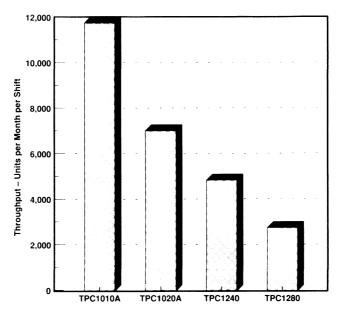

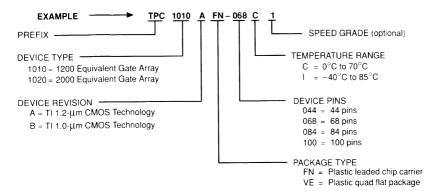

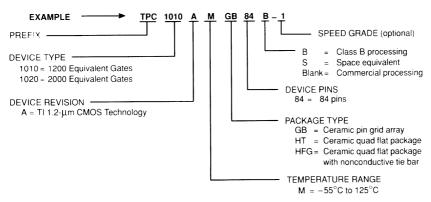

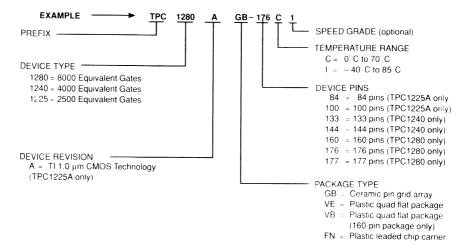

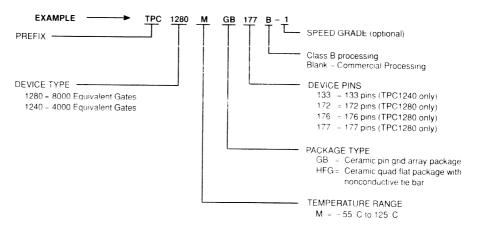

This family of products contains three series of devices: TPC10, TPC12, and TPC14. The TPC10 Series offers four devices: TPC1010A and TPC1020A (1.2-μm double-level metal technology) and TPC1010B and TPC1020B (1.0-μm double-level metal technology). These devices provide a capacity of 1200 and 2000 gate array equivalent gates respectively. The TPC12 Series offers three devices: TPC1225A with 2500 gates, TPC1240 with 4000 gates, and the TPC1280 with 8000 gates. The TPC14 Series family offers gate capacities ranging from less than 1000 to greater than 10,000 gate array equivalent gates.

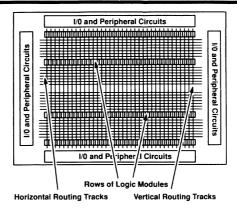

At the heart of TI's FPGA devices are the logic modules. These modules can be used to generate an array of logic gates from simple generic gates to more complicated circuits. The TPC10 Series devices use a combinatorial logic module, while the TPC12 and TPC14 Series devices use both a combinatorial and a sequential logic module. The number of logic modules used in each design vary among devices. The family's die architecture consists of rows of logic modules separated by routing tracks.

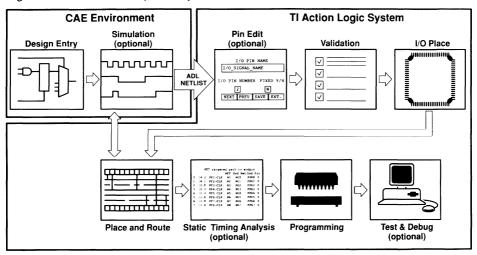

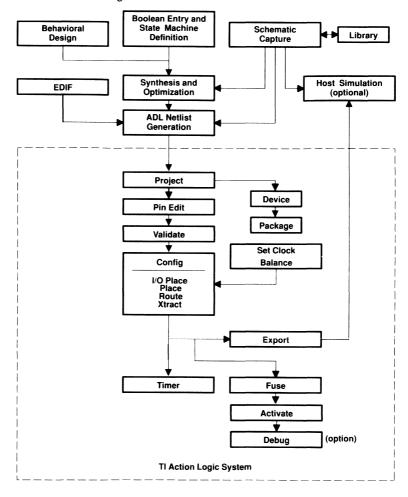

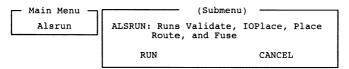

In addition to innovative hardware technology, designers with TI FPGAs use the Texas Instruments Action Logic™ System (TI-ALS) as their software design environment. Users are able to design with a variety of popular input methods on several different hardware platforms. TI-ALS then provides automatic placement and routing, timing analysis, programming capability, and functional test and debug with the ability to observe internal signals.

This book contains more detailed information on the TPC10, TPC12, and TPC14 Series product data, available TI-ALS hardware and software systems and their product descriptions, TI-ALS design flow, and general applications information.

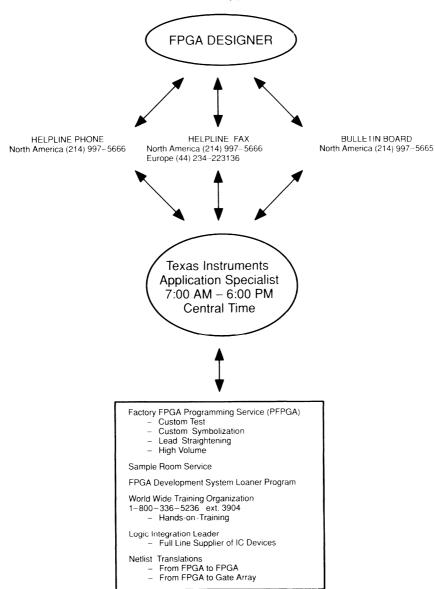

For more information on TI's FPGA family contact your local TI Field Sales Office, TI Authorized Distributor, or call the Texas Instruments FPGA helpline at (214) 997-5666.

# **Preface**

# **Read This First**

#### About This Manual

This data manual provides detailed information on the Texas Instruments TPC Series FPGA CMOS devices. The following list summarizes the contents of the chapters in this book.

# How to Use This Manual

This document contains the following chapters:

# Chapter 1 General Information

Includes a glossary of electrical and FPGA-related terms used throughout this manual. Provides a TI FPGA product selection summary and a general overview of the TPC Series architecture.

# Chapter 2 TPC FPGA Series Data

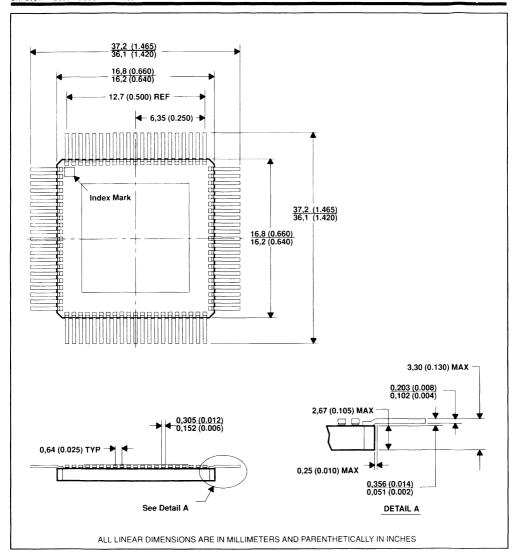

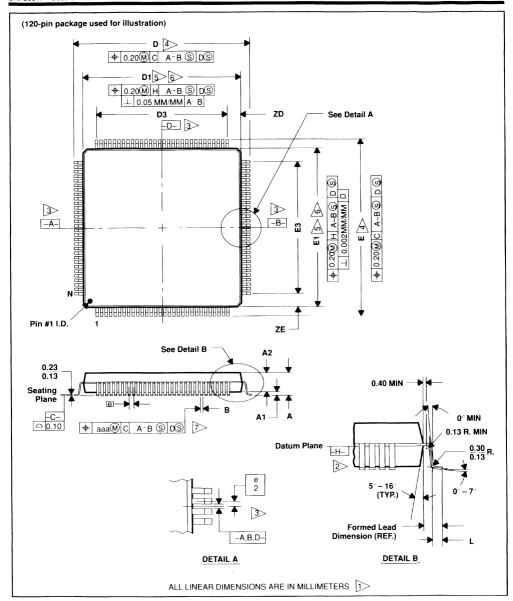

Presents the TPC10 and TPC12 Series individual datasheets which contain electrical and switching characteristics, mechanical drawings and packaging options, and supported library macro listings and symbols for each of the TPC Series families. Includes the TPC10 and TPC12 macro pin loading tables as well as a product preview of the TPC14 Series.

# Chapter 3 Action Logic System Overview

Contains an overview of the TI-ALS development system environment, TI third party support, and hardware programming and debug tools. Details a step-by-step design flow through the TI-ALS software.

# Chapter 4 FPGA Design Software and Hardware

Lists the TI-ALS system configurations and software/hardware options and provides detailed system descriptions of all the available configurations.

# Chapter 5 Quality and Reliability Data

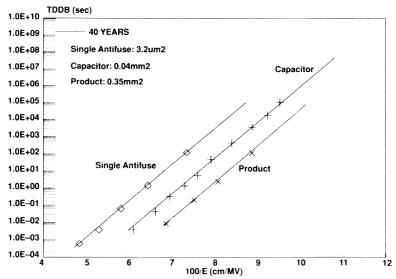

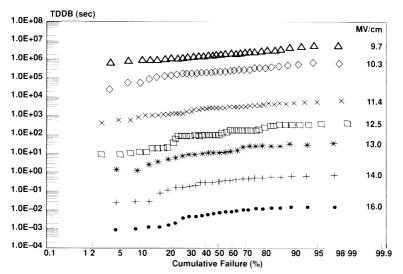

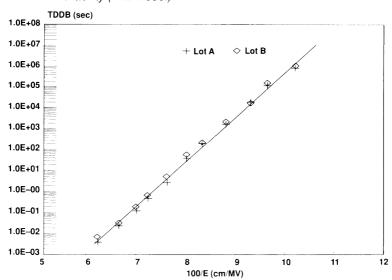

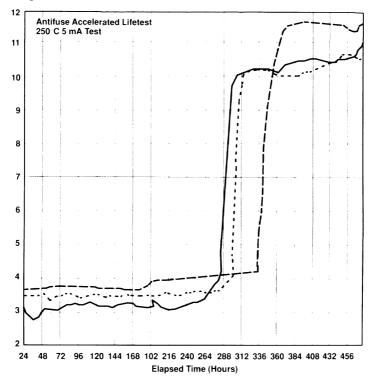

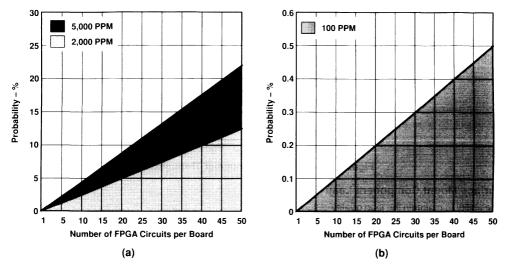

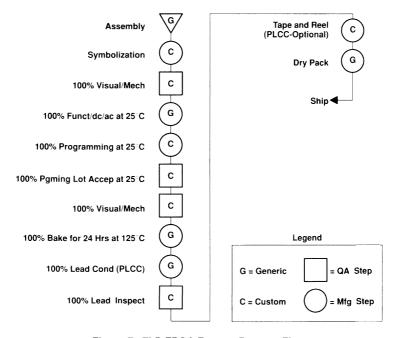

Provides antifuse reliability studies and graphs, under license from Actel Corporation. Details the Texas Instruments quality and reliability tests and their data reports for the TPC Series FPGA products.

| Chapter 6 | Applications Discusses the following FPGA applications:                                                                                                                                                                                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

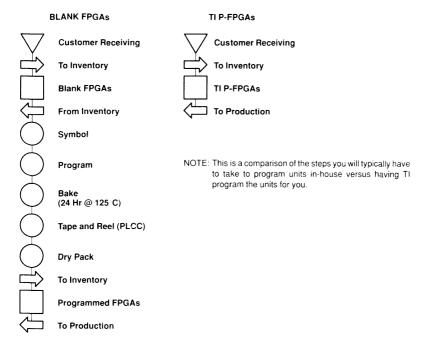

|           | <ul> <li>Critical Path Analysis for Field-Programmable Gate Arrays</li> <li>Programming Field-Programmable Gate Arrays: Manufacturing Considerations and Options</li> <li>How TI Tests Field-Programmable Gate Arrays</li> <li>IEEE 1149.1 Boundary Scan Library Components</li> </ul> |

| Chapter 7 | Ordering Information Includes the ordering information for all the TPC Series development systems, hardware options, and device silicon                                                                                                                                                |

### Trademarks

ABEL-FPGA is a trademark of Data I/O Corporation

Action Logic, Activator, Actionprobe, PLICE, and APS are trademarks of Actel Corporation

AllPRO is a trademark of Logic Devices, Inc.

Apollo is a trademark of HP/Apollo Computer, Inc.

Cadence and Valid are trademarks of Cadence Design Systems, Inc.

Design Compiler is a trademark of Synopsys, Inc.

Mentor is a trademark of Mentor Graphics Corporation

OrCAD and OrCAD/SDT III are trademarks of OrCAD Systems Corporation

PAL is a registered trademark of Advanced Micro Devices Inc.

PGADesigner is a trademark of Minc Incorporated

Sun is a trademark of Sun Microsystems, Inc.

Viewlogic, Viewdraw, Viewsim, Viewwave are trademarks of Viewlogic Systems Inc.

vi Read This First

| General Information               | 1 |

|-----------------------------------|---|

| TPC FPGA Series Data              | 2 |

| Action Logic System Overview      | 3 |

| FPGA Design Software and Hardware | 4 |

| Quality and Reliability Data      | 5 |

| Applications                      | 6 |

| Ordering Information              | 7 |

# **Chapter 1**

# **General Information**

Includes a glossary of electrical and FPGA-related terms used throughout this manual. Provides a TI FPGA product selection summary and a general overview of the TPC Series architecture.

#### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

#### PART 1 — GENERAL CONCEPTS AND CLASSIFICATIONS OF CIRCUIT COMPLEXITY

#### ADL

Design language. The format for TI-ALS design data.

#### ALS

Action Logic System.

# Action Logic™ System

The development system for configuring, programming, and debugging TI FPGAs.

#### **Actionprobe**™

TI-ALS feature that allows internal circuit nodes to be observed at the external device pin.

#### **Activate**

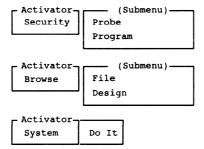

TI-ALS program that programs the TPC device.

#### Activator™ 1

Programming hardware for TPC10 Series devices.

#### Activator™ 2

Programming hardware for all current and planned TPC Series devices. Supports programming up to four devices at a time.

### Activator™ 2S

Programming hardware for all current and planned TPC Series devices. Supports programming of one device at a time.

#### **Antifuse**

A term for the type of programming element used in TPC arrays. An antifuse is an element which is normally open, but converts to a resistive connection when programmed.

# Array

The area occupied by the rows of modules and the routing channels.

#### Assertion

System error causing abnormal program termination. A failure code is written to the \alsuser\user\user\user\lagsert.log file. Errors of this type should be reported to the TI FPGA helpline, (214) 997-5666.

#### **Back Annotation**

The process of translating data generated from the TI-ALS system back to the CAE design environment. Postlayout delay information is back annotated to the CAE simulator.

#### **Binning Circuit**

Nonuser circuit used to characterize the AC performance of a TPC device. All TPC devices contain a binning circuit that has been tested to an AC test limit to ensure data sheet specifications have been met.

#### Channel

The area reserved for routing; containing horizontal tracks and horizontal pass transistors.

#### Clock Network

A system for distributing a global clock signal throughout the array, with minimum skew and large drive capability.

#### Configure

Process for determining placement and routing for a design.

#### **Critical Net**

Net whose signal propagation delay is part of a critical path in the design.

#### Criticality

Design property. The level of criticality assigned influences the placement and routing of a net and may influence the propagation delay associated with the net. The four levels of criticality are fast critical (F), medium critical (M), uncritical (U) and default critical.

#### Criticality File

Design constraint file for assigning criticality to nets.

#### DCLK Pin

Device pin. When MODE = 0, DCLK is a user I/O, and when MODE = 1, DCLK is used by the program/debug hardware to clock data into internal program/test registers.

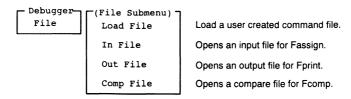

# Debugger

TI-ALS program for debugging programmed TPC devices.

#### Designer

The component of the TI-ALS system which validates, configures, and generates fuse files for FPGA designs for devices up to 2500 gates.

#### **Designer Advantage**

The component of the TI-ALS system which validates, configures, and generates fuse files for FPGA designs for devices up to 10,000 gates.

#### Error

A design problem that must be corrected before TI-ALS will proceed.

# **Extract**

TI-ALS program that creates postlayout delay information.

#### **Fixed Macro**

A hard macro that has a user-assigned location in the array that is not altered by automatic placement.

#### **Fusemap**

Design file containing a list of antifuse addresses used by the programming hardware to program the device.

# Fuser

TI-ALS program that generates the fusemap for the TPC device.

# **Gate Equivalent Circuit**

A basic unit of measure of relative digital circuit complexity. The number of gate equivalent circuits is that number of individual logic gates that would have to be interconnected to perform the same function.

#### GND

Device pin. All pins labeled GND must be connected to circuit ground.

#### **Hard Macro**

Unit-level macros that have a fixed relative placement. Two-module hard macros are always placed in modules which are side by side. All routing between two-module hard macros is predetermined. Hard macros are predefined by Texas Instruments.

# Hierarchy

Style of organizing a design where a level of a logic design is expressed in terms of lower-level subcircuits or blocks. Lower-level blocks may, in turn, be expressed in terms of other lower-level blocks.

#### ICP

In circuit probe debugger command used to assign the Actionprobes to signals internal to a TPC device operating in the end system environment.

#### I/O Module

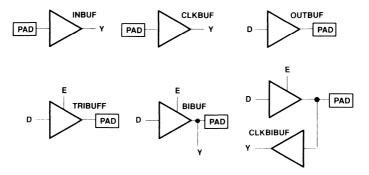

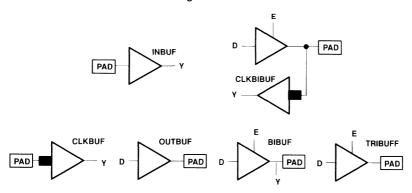

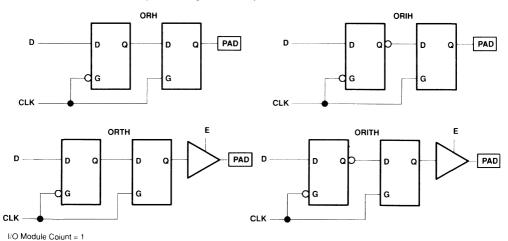

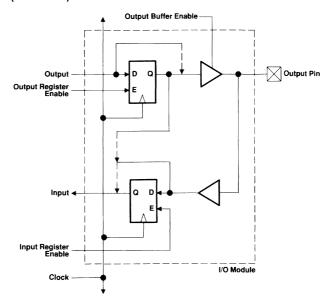

Module used to configure I/O macros, like INBUF, TRIBUFF, etc.

#### I/O Pin

The connection to the package lead that is bonded to the device I/O buffer.

#### Instance

CAE term. Each placement of a library element or hierarchical block into a design defines a unique instance of that element. The instance may have a default or assigned name that is independent of the library element function.

#### Instance Pins

An instance pin is a macro pin for a given instance. For example, the A input of an AND2A (2-input and gate) with an instance name of U1 has an instance pin name of U1:A.

#### Label

CAE term. A label is a method of attaching names, text, etc., to nets or instances in a design.

#### Level

A property attached to macro symbols indicating which category of macros they belong to. Choices are unit, hard, soft, and user.

#### **Logic Compaction**

Logic compression; logic conversion from standard TTL or CMOS technology into TI FPGA technology which combines functions from multiple logic elements into one logic module.

# **Logic Module**

Module used to configure logic macros, like AND, OR, etc. The basic logic building block of the TI-FPGA from which all logical functions are built.

# Long Horizontal Track

A horizontal routing track is used to interconnect two (or more) pins on a net that are separated by a substantial horizontal distance. Typically, a long horizontal track occupies more than a third of the columns of the array. Only a limited number of such tracks are available. If more tracks are needed, the placement will fail. Nets using long horizontal tracks may encounter some additional delay.

### Long Vertical Track

A vertical routing track is used to interconnect two (or more) pins on a net that are separated by a substantial vertical distance. Typically, a long vertical track occupies more than three to six rows of the array. Only a limited number of tracks are available. If more tracks are needed, the placement will fail. Nets using long vertical tracks may encounter a substantially longer delay than the median.

#### Macro Pin

Macro pins are connection points to macro functions. For example, the A input of an AND2A (2-input and gate) is a macro pin.

#### Mode Pin

Device pin which places the device in normal mode (MODE=0) or test/program mode (MODE=1).

#### Module

Synonym for the basic functional block in a TPC array. Modules are used to construct macros. (See Logic Module).

#### Net

A logic signal path between macros. A net can be implemented in one or more routing segments connected by two or more antifuses.

# PRA, PRB (or MPRA, MPRB)

Device pin. When MODE=1, PRA and PRB function as Actionprobe pins. When MODE=0, PRA and PRB are user-defined I/O pins.

#### Place

TI-ALS program that determines the placement of the design logic into logic modules in the TPC arrays.

# Programmable Array Logic (PAL)

PAL® circuits are user programmable integrated circuits which utilize fuse link technology to implement logic functions. Implements sum of products logic by using a programmable AND array whose outputs feed a fixed OR array.

#### Route

TI-ALS program that determines the interconnection of logic modules in TPC arrays.

#### Row

A horizontal tile of logic modules; the lowest row in the array is row 0 (zero). Channel n is always below row n.

#### SDI

Device pin. When MODE=0, SDI is a user I/O, and when MODE=1, SDI is used by the program/debug hardware as a serial data input for internal program/test registers.

# **GLOSSARY**

#### SDO

Device pin. Same as above except SDO in place of SDI and serial data output. TPC12 Series only.

#### Security Fuse

Special antifuses for providing user security of TPC devices after programming.

#### Segment

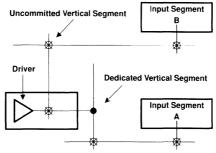

A piece of wire used for routing. It is connected by one or more antifuses to other segments in either the same or perpendicular direction. Horizontal segments run horizontally in the channels. Vertical segments run vertically through the modules and are often dedicated (connected to a module input or output).

#### **Short Path**

A chain of a small number (usually less than five) of macros connected by up to three nets. The chain of nets need NOT be a signal path, that is, the path can go from one input pin to another, or the nets can carry signals in opposite directions.

#### Soft Macro

Predefined blocks consisting of multiple hard and/or unit and/or other soft macros. Placement and routing is not predetermined for soft macros.

#### Stretched Short Path

A short path where the first and the last macros in the chain are fixed macros and are located so far apart that at least one of the nets in this path must use a long horizontal and/or long vertical routing track..

#### **TI-ALS**

Texas Instruments Action Logic System.

#### TPC10

FPGA family consisting of the TPC1010 and TPC1020 devices.

#### TPC12

FPGA family consisting of the TPC1225, TPC1240, and TPC1280 devices.

#### TPC14

FPGA family in preliminary form designed as a third generation TI product.

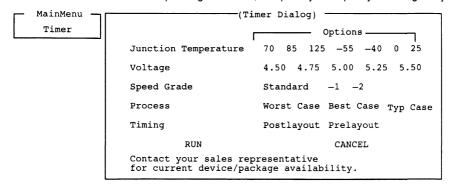

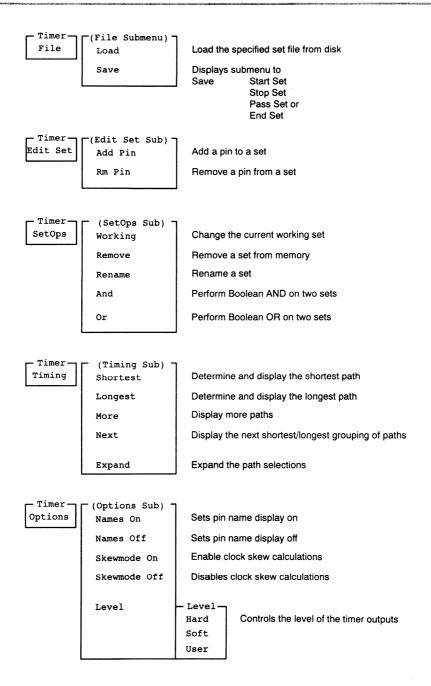

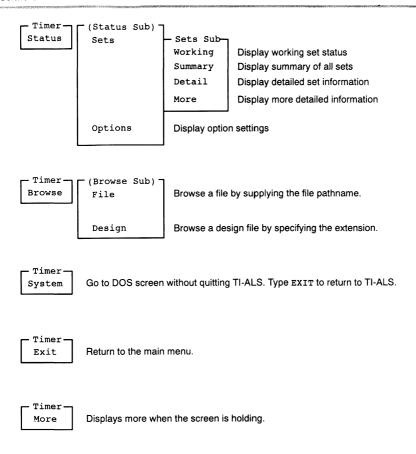

# Timer

TI-ALS program for performing static timing analysis on TPC devices.

#### Track

A set of segments connected end-to-end, running across the array in the vertical or horizontal direction. The segments may or may not be connected by antifuses.

#### **Unit Macro**

A cell from the TI macro library implemented in one logic module. A unit-level macro can be implemented in any of several ways by the configuration software.

### User Macro

A customer designed block consisting of multiple and/or unit hard macros and/or soft macros or other user macros. Placement and routing is not predetermined. User is the default if no LEVEL property is attached.

$v_{cc}$

Device pin. All pins labeled V<sub>CC</sub> must be connected to the 5-V power supply.

$v_{KS}$

Device pin. During programming, a "keeper supply" voltage is applied to  $V_{KS}$ . During normal operation this pin must be tied to circuit ground.

$V_{PP}$

Device pin. During programming, high voltage is applied to  $V_{PP}$ . During normal operation, this pin must be tied to  $V_{CC}$  level.

$v_{sv}$

Device pin. During programming, a "super" voltage is applied to  $V_{SV}$ . During normal operation, this pin must be tied to  $V_{CC}$  level.

Warning

A nonfatal message that alerts you to a situation that may cause problems or difficulties, if not corrected.

# PART 2 — OPERATING CONDITIONS AND CHARACTERISTICS (IN SEQUENCE BY LETTER SYMBOLS)

### C<sub>i</sub> Input capacitance

The internal capacitance at an input of the device.

# Co Output capacitance

The internal capacitance at an output of the device.

# f<sub>clock</sub> Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

# I<sub>CC</sub> Supply current

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit.

# I<sub>CCH</sub> Supply current, outputs high

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit when all (or a specified number) of the outputs are at the high level.

# I<sub>CCL</sub> Supply current, outputs low

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit when all (or a specified number) of the outputs are at the low level.

# I<sub>IH</sub> High-level input current

The current into\* an input when a high-level voltage is applied to that input.

# I<sub>IL</sub> Low-level input current

The current into\* an input when a low-level voltage is applied to that input.

# IOH High-level output current

The current into\* an output with igput conditions applied that, according to the product specification, will establish a high level at the output.

# I<sub>OL</sub> Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a low level at the output.

# IOS (IO) Short-circuit output current

The current into\* an output when that output is short-circuited to ground (or other specified potential) with input conditions applied to establish the output logic level farthest from ground potential (or other specified potential).

#### loz

The current flowing into\* an output having 3-state capability with input conditions established that, according to the production specification, will establish the high-impedance state at the output.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is guaranteed.

<sup>\*</sup> Current out of a terminal is given as a negative value

# I<sub>OZH</sub> Off-state (high-impedance-state) output current (of a three-state output) with high-level voltage applied

The current flowing into\* an output having 3-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output and with a high-level voltage applied to the output.

NOTE: This parameter is measured with other input conditions established that would cause the output to be at a low level if it were enabled.

# I<sub>OZL</sub> Off-state (high-impedance-state) output current (of a three-state output) with low-level voltage applied

The current flowing into\* an output having 3-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output and with a low-level voltage applied to the output.

NOTE: This parameter is measured with other input conditions established that would cause the output to be at a high level if it were enabled.

# VIH High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is guaranteed.

# V<sub>IK</sub> Input clamp voltage

An input voltage in a region of relatively low differential resistance that serves to limit the input voltage swing.

# V<sub>IL</sub> Low-level input voltage

An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### V<sub>OH</sub> High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a high level at the output.

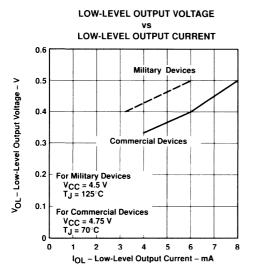

#### V<sub>OL</sub> Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a low level at the output.

# t<sub>a</sub> Access time

The time interval between the application of a specific input pulse and the availability of valid signals at an output.

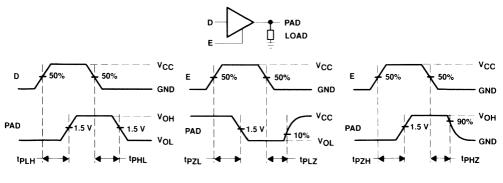

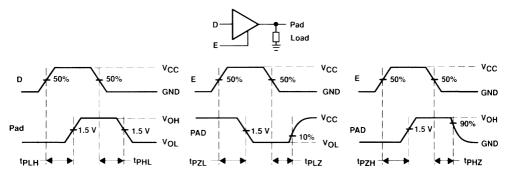

# t<sub>dis</sub> Disable time (of a 3-state output)

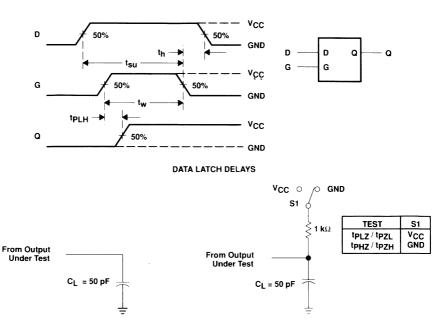

The time interval between the specified reference points on the input and output voltage waveforms, with the 3-state output changing from either of the defined active levels (high or low) to a high-impedance (off) state.  $(t_{dis} = t_{PHZ} \text{ or } t_{PLZ})$ .

<sup>\*</sup> Current out of a terminal is given as a negative value

# ten Enable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from a high-impedance (off) state to either of the defined active levels (high or low). ( $t_{en} = t_{PZH}$  or  $t_{PZL}$ ).

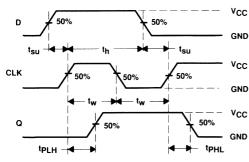

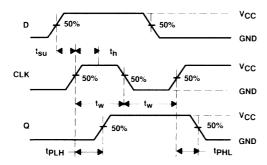

# th Hold time

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

- NOTES 1: The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is guaranteed.

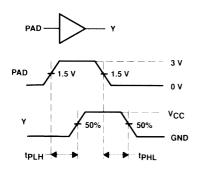

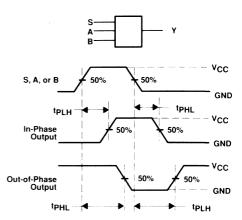

# tpd Propagation delay time

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level. ( $t_{\text{pd}} = t_{\text{PHL}}$  or  $t_{\text{PLH}}$ ).

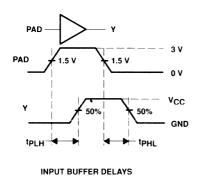

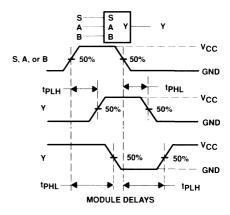

# tpHI Propagation delay time, high-to-low level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level.

# t<sub>PHZ</sub> Disable time (of a three-state output) from high level

The time interval between the specified reference points on the input and the output voltage waveforms with the three-state output changing from the defined high level to a high-impedance (off) state.

### tpl H Propagation delay time, low-to-high level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level.

# t<sub>PLZ</sub> Disable time (of a three-state output) from low level

The time interval between the specified reference points on the input and the output voltage waveforms with the three-state output changing from the defined low level to a high-impedance (off) state.

# tpzH Enable time (of a three-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined high level.

#### tp71 Enable time (of a three-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined low level.

#### tsk(o) Output Skew

The time interval between any two propagation delay times when a single switching input or multiple inputs switching simultaneously causes multiple outputs to switch, as observed across all switching outputs.

# t<sub>su</sub> Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

- NOTES 1: The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- 2. The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

# tw Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

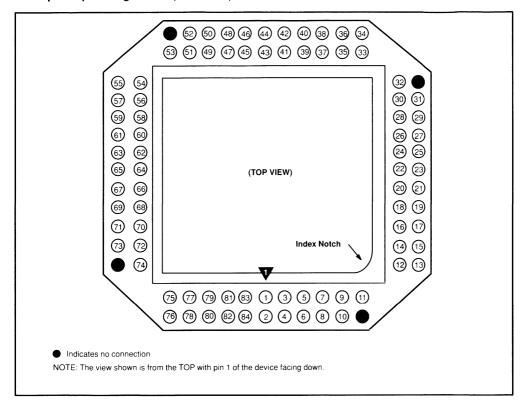

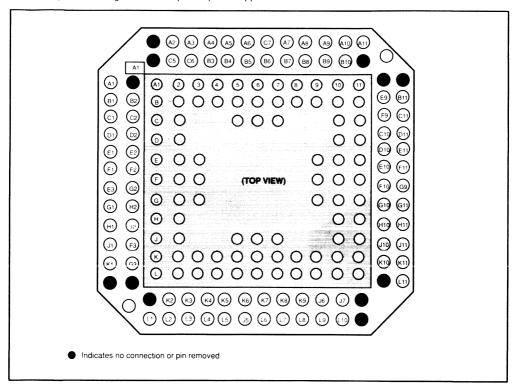

| TPC DEVICE | PACKAGE | NO of PINS | SPEED<br>OPTION | PROCESS | GATE ARRAY<br>GATES |

|------------|---------|------------|-----------------|---------|---------------------|

| TPC1010A   | FN      | 44         | STD, -1         | C, I    | 1200                |

|            | FN      | 68         | STD, -1         | C, I    | 1200                |

|            | GB      | 84         | STD             | M, B    | 1200                |

|            | HT      | 84         | STD             | M, B    | 1200                |

|            | VE      | 100        | STD, -1         | C, I    | 1200                |

| TPC1010B   | FN      | 44         | STD, -1         | C, I    | 1200                |

|            | FN      | 68         | STD, -1         | C, I    | 1200                |

|            | VE      | 100        | STD, -1         | C, I    | 1200                |

| TPC1020A   | FN      | 44         | STD, -1         | C, I    | 2000                |

|            | FN      | 68         | STD, ~1         | C, I    | 2000                |

|            | FN      | 84         | STD, ~1         | C, I    | 2000                |

|            | GB      | 84         | STD, -1         | M, B    | 2000                |

|            | HT      | 84         | STD, -1         | M, B, S | 2000                |

|            | VE      | 100        | STD, -1         | C, I    | 2000                |

| TPC1020B   | FN      | 44         | STD, -1         | C. I    | 2000                |

|            | FN      | 68         | STD, -1         | C, I    | 2000                |

|            | FN      | 84         | STD, -1         | C, I    | 2000                |

|            | VE      | 100        | STD, -1         | C, I    | 2000                |

| TPC1225A   | FN      | 84         | STD, -1         | C, I    | 2500                |

|            | VE      | 100        | STD, -1         | C, I    | 2500                |

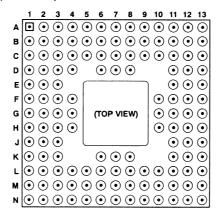

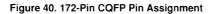

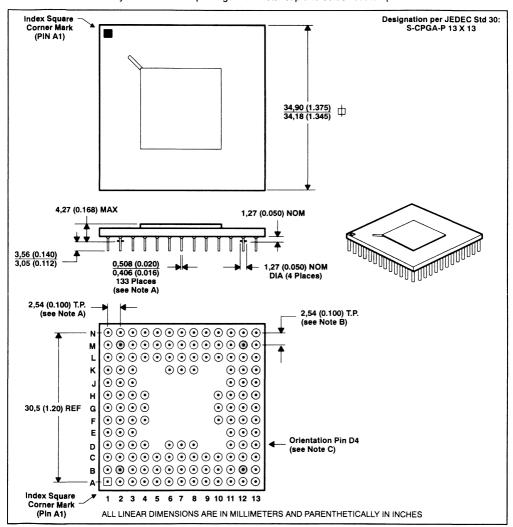

| TPC1240    | GB      | 133        | STD             | C, I, M | 4000                |

|            | VE      | 144        | STD             | C, I    | 4000                |

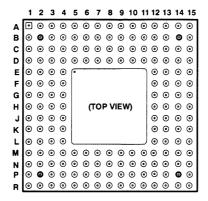

| TPC1280    | GB      | 176        | STD, -1         | C, I    | 8000                |

|            | GB      | 177        | STD, -1         | C, I, M | 8000                |

|            | HFG     | 172        | STD             | M       | 8000                |

|            | VB      | 160        | STD, -1         | C, I    | 8000                |

| TPC1425    | FN      | 84         | STD             | С       | 2500                |

|            | GB      | 133        | STD             | C, I    | 2500                |

|            | VE      | 160        | STD             | C       | 2500                |

| TPC1460    | GB      | 207        | STD             | C, I    | 6000                |

|            | VE      | 208        | STD             | C       | 6000                |

# Legend:

Package Types: VB - Plastic Quad Flat Pack

VE - Plastic Quad Flat Pack GB - Ceramic Pin Grid Array

FN - Plastic Leaded Chip Carrier HT - Ceramic Quad Flat Pack

HFG - Ceramic Quad Flat Pack with nonconductive tie bar

Speed Options: STD - Standard Speed

-1 - Standard - 15% Faster

Process: С - Commercial (0°C to 70°C)

> - Industrial (-40°C to 85°C) 1

Military (–55°C to 125°C) M

- MIL-STD-883C В

- Space Equivalent

#### INTRODUCTION

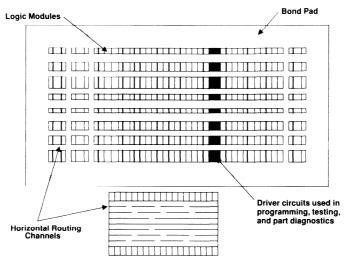

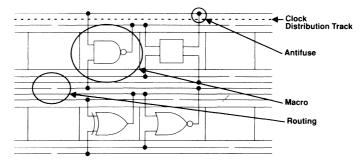

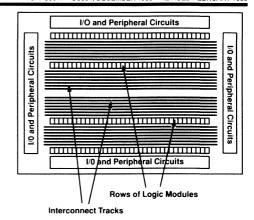

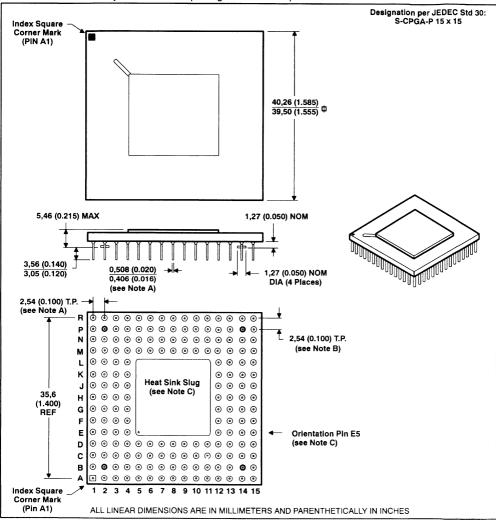

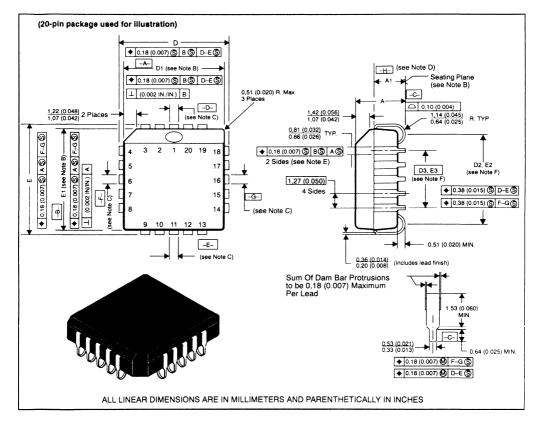

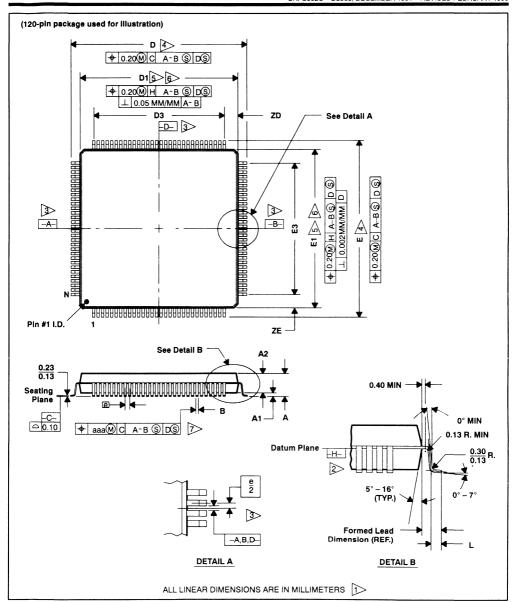

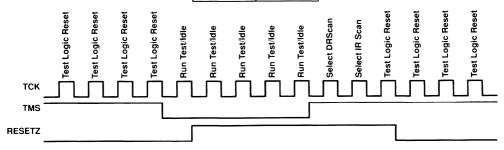

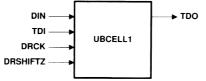

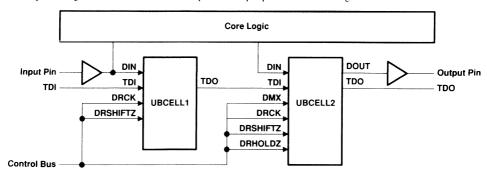

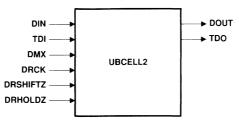

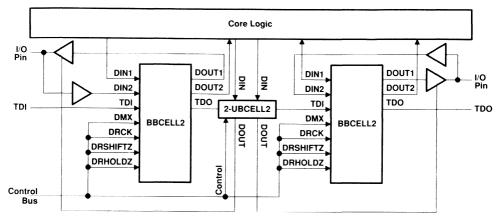

To develop an understanding of the capabilities of a field programmable gate array (FPGA), a knowledge of its architectural elements is needed; see Figure 1–1 and Figure 1–2. TI FPGAs have several characteristic features which define their function. These basic features are the antifuse, the logic module, the clock distribution network, routing channels, and diagnostic circuits.

Figure 1-1. Device Architecture

Figure 1-2. Architecture Detail

### **Architectural Overview**

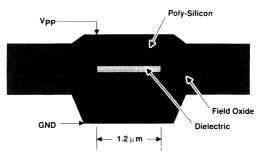

#### The Antifuse

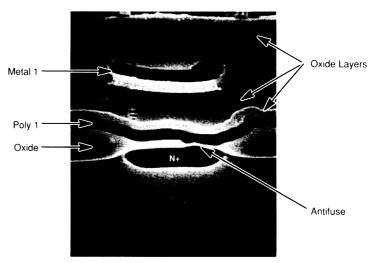

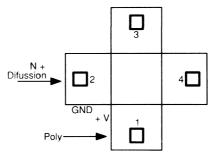

The element which provides programmability to the device is the antifuse, which is shown in Figure 1–3. An antifuse is a normally open device which becomes conductive when a high voltage pulse is applied to it. This is opposite to the action of a fuse which becomes nonconductive when a large voltage or current is applied to it. As Figure 1–3 shows, the antifuse consists of two conducting layers separated by a thin isolation layer. Another important feature is the small size which is up to 19 times smaller than other types of programmable elements such as EEPROM or SRAM

Figure 1-3. FPGA Antifuse

Metal routing tracks run horizontally and vertically over the die, with an antifuse at each intersection. The unprogrammed resistance of the antifuse is greater than 100 M $\Omega$  and the programmed resistance is approximately 500  $\Omega$ .

#### Routing

As Figure 1–1 and Figure 1–2 shows, the FPGA architecture is analogous to that of a channeled gate array with routing tracks running horizontally between the logic modules and vertically over them. These tracks connect the macro functions implemented in the logic modules. The number of routing tracks per channel is family dependent and the segmentation of these tracks varies from device to device. Segmentation refers to the varying length of tracks in a routing channel.

# **Logic Module**

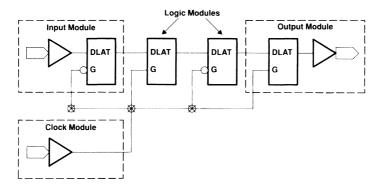

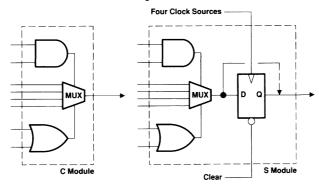

A prominent feature of the architecture is the rectangular array of logic modules which contain generic logic circuits. These circuits can be programmed to perform a variety of functions. Each logic module is multiplexer based. A TPC10 Series device has only one type of combinatorial logic module. Sequential TPC10 Series functions are implemented using combinatorial modules. The TPC12 and TPC14 Series device families have both the combinatorial module and an enhanced sequential module.

The macro functions implemented in the logic modules are generated in several ways. They come from TI-supplied hard and soft macro libraries or can be created by the user.

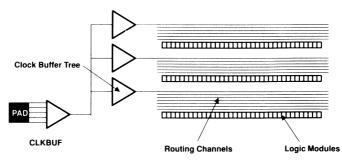

### **Clock Distribution**

High drive requirements for the clock signal are met by a dedicated clock buffer network which is shown in Figure 1–4. This network consists of an assigned input pin and row buffers to provide additional drive for the large fan-out requirements of the clock signal. The network can connect to any logic module but only to clock and gated inputs of sequential macro functions.

Figure 1-4. Dedicated Clock Buffer Network

# **Test and Debug Diagnostics**

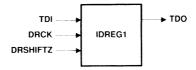

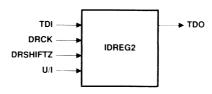

Special circuitry is built into the device for diagnostics. This circuitry consists of shift registers which allow the user to address and probe any internal node of the programmed device. Four special I/O pins are provided for this function. These pins are multiplexed so that they can be configured as diagnostic or normal I/O pins and are controlled by the debug function of the TI Action Logic™ System (TI-ALS). This function allows any two internal nodes to be probed simultaneously while the device is operating in an actual circuit board.

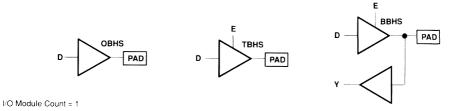

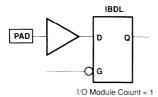

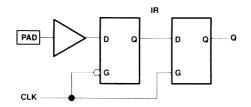

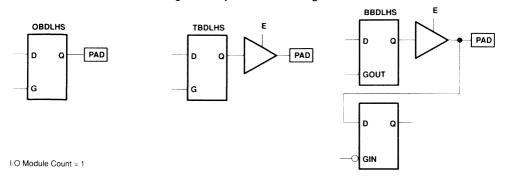

# Inputs/Outputs

The I/O count depends on the device and the packaging of the device. The I/O function can be programmed as either input, output, 3-state, or bidirectional.

| General Information               | 1 |

|-----------------------------------|---|

| TPC FPGA Series Data              | 2 |

| Action Logic System Overview      | 3 |

| FPGA Design Software and Hardware | 4 |

| Quality and Reliability Data      | 5 |

| Applications                      | 6 |

| Ordering Information              | 7 |

# **Chapter 2**

# **TPC FPGA Series Data**

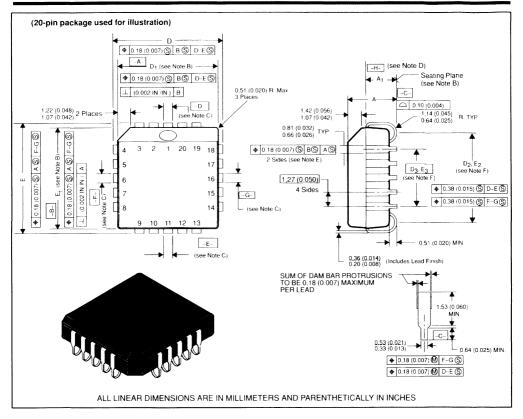

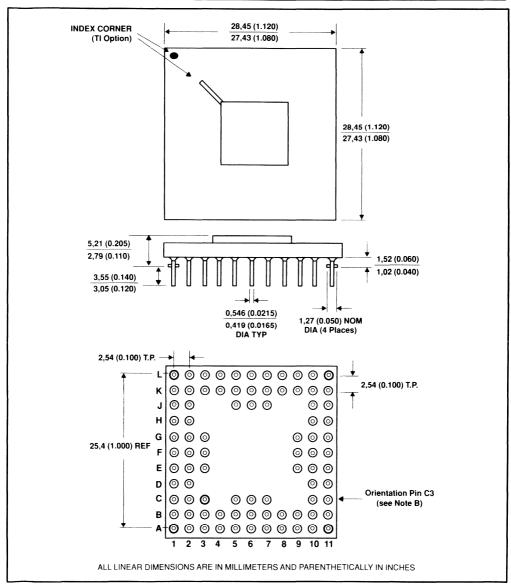

Presents the TPC10 and TPC12 Series individual datasheets which contain electrical and switching characteristics, mechanical drawings and packaging options, and supported library macro listings and symbols for each of the TPC Series families. Includes the TPC10 and TPC12 macro pin loading tables as well as a product preview of the TPC14 Series.

2-4 TPC FPGA Series Data

- Four Arrays With up to 2000 Usable Equivalent Gates

- TI Action Logic™ System (TI-ALS) Software for:

- ViewLogic ™

- Mentor™

- OrCAD/SDT III ™

- Cadence™/Valid™

- Reliable Antifuse Interconnect

- Built-In Clock Distribution Network

- Silicon-Gate CMOS Technology

- Desktop TI-ALS Creates Design Files for:

- I/O Pin Assignment

- Design Validation

- Place and Route

- Circuit Timing Analysis

- Array Antifuse Programming

- Test and Debug

TPC10 Series FPGA Die Architecture

# description

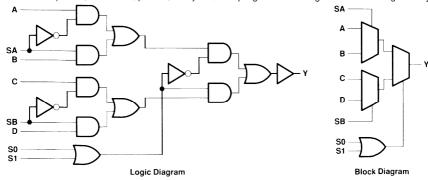

The Texas Instruments (TI) TPC10 Series comprises four field-programmable gate arrays (FPGAs). The TPC1010A, TPC1010B, TPC1020A, and TPC1020B FPGAs are fabricated using the TI silicon-gate CMOS process. The process features polysilicon gate, source, drain elements, and two levels of copper-doped-aluminum metallization to reduce internal resistance and enhance performance. Typical die architecture is illustrated above.

These field-programmable devices combine gate-array flexibility with desktop programmability. This combination allows the designer to avoid fabrication cycle times and nonrecurring engineering charges associated with conventional mask-programmed gate arrays. The FPGAs are unique in that the arrays are fabricated, tested, and shipped to the user for programming. The FPGA contains user-configurable inputs, outputs, logic modules, and minimum-skew clock driver with hardwired distribution network. The FPGA also includes on-chip diagnostic probe capabilities and security fuses to protect the proprietary design.

**Table 1. Product Family Profile**

| DEVICE                      | TPC1010A | TPC1020A | TPC1010B | TPC1020B |

|-----------------------------|----------|----------|----------|----------|

| Capacity                    |          |          |          |          |

| Gate array equivalent gates | 1200     | 2000     | 1200     | 2000     |

| TTL equivalent packages     | 34       | 53       | 34       | 53       |

| CMOS Process                | 1.2 μm   | 1.2 µm   | 1.0 μm   | 1.0 μm   |

| Logic Modules               | 295      | 547      | 295      | 547      |

| Flip-Flops (maximum)        | 130      | 273      | 130      | 273      |

| Antifuses                   | 112,000  | 186,000  | 112,000  | 186,000  |

| Horizontal Tracks           | 22       | 22       | 22       | 22       |

| Vertical Tracks             | 13       | 13       | 13       | 13       |

Action Logic, Activator, and Actionprobe are trademarks of ACTEL Corporation. Cadence/Valid are trademarks of Cadence Design Systems, Inc. Mentor is a trademark of Mentor Graphics Corporation. OrCAD/SDT III is a trademark of OrCad Systems Corporation. ViewLogic is a trademark of Viewlogic System, Incorporated.

Copyright © 1993, Texas Instruments Incorporated

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

# Action Logic System (ALS) and Activator

TPC10 Series FPGAs are supported by the ALS software and Activator™ programming hardware. The combination facilitates logic design and FPGA programming on popular CAE workstations with minimum effort. ALS interfaces to the resident CAE system providing a complete library of TPC10 Series functions. The ALS includes automatic place and route, timing verification, and FPGA device programming. The ALS and Activator are available for ViewLogic or OrCAD (SDT III) 386/486 based PC systems, Mentor-equipped Apollo workstations, and ViewLogic- or Valid/Cadence-equipped Sun-4 workstations.

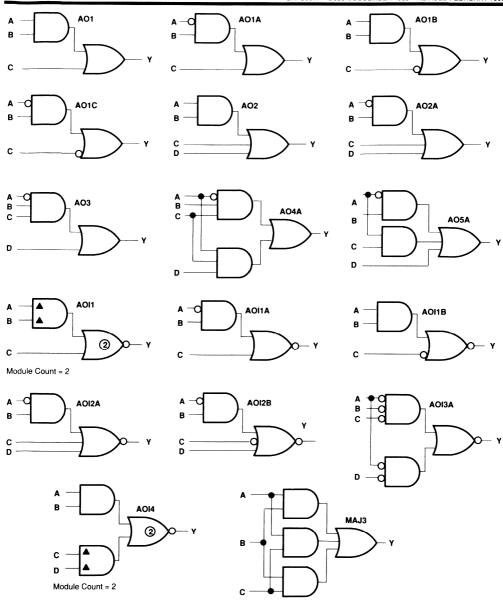

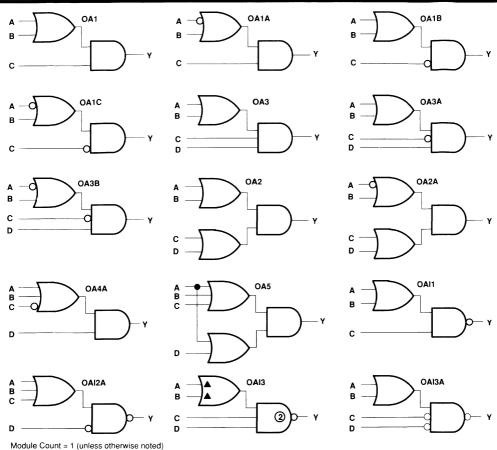

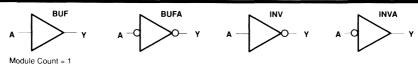

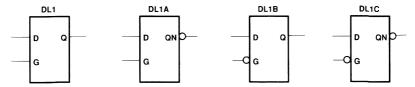

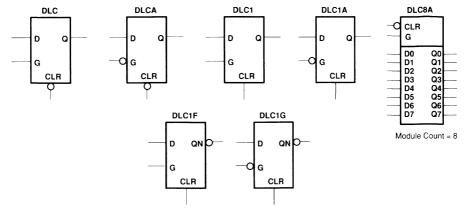

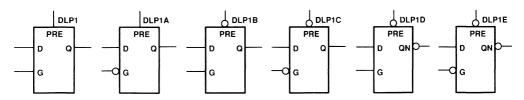

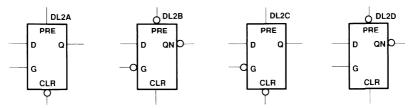

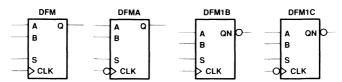

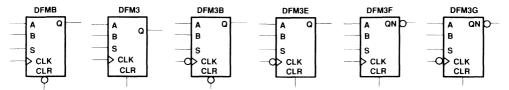

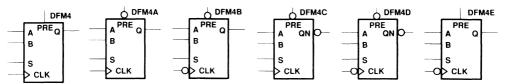

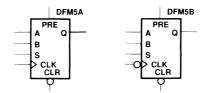

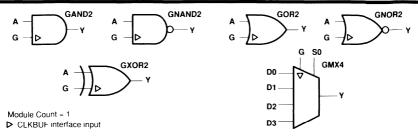

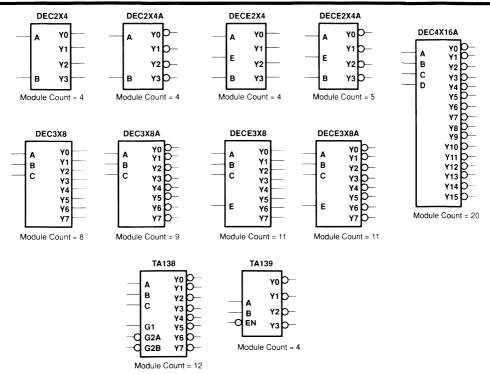

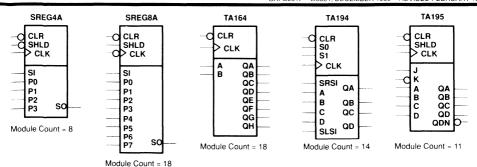

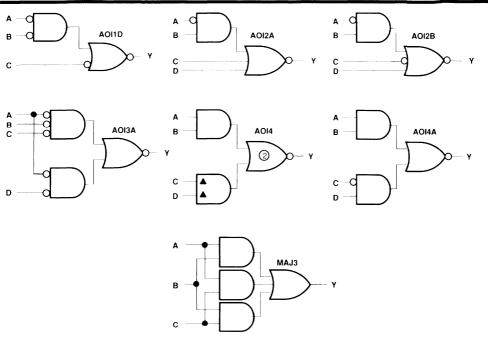

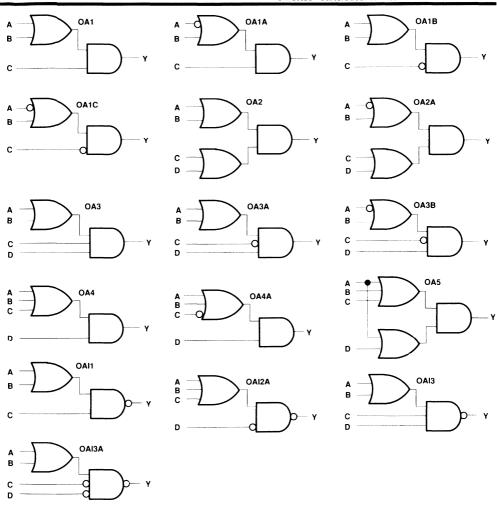

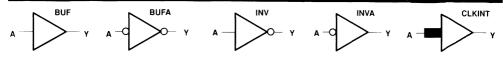

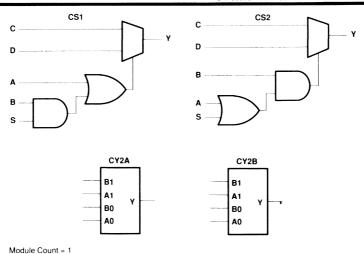

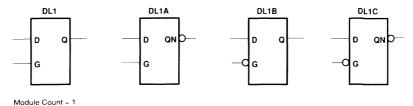

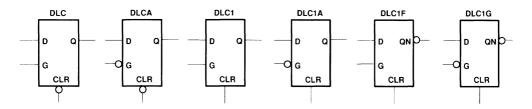

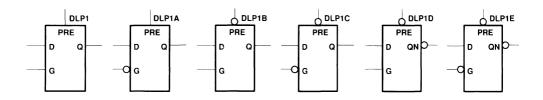

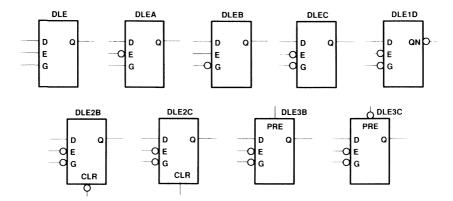

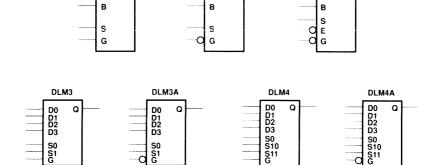

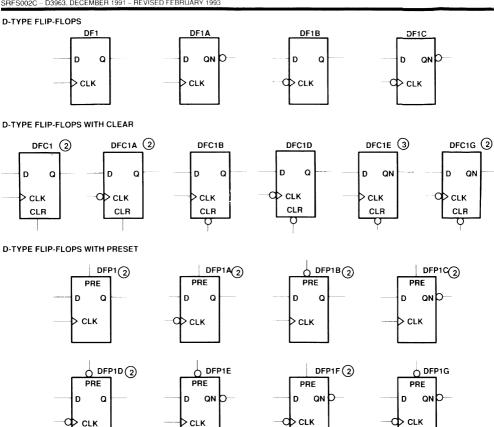

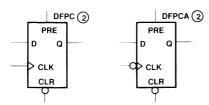

# library functions

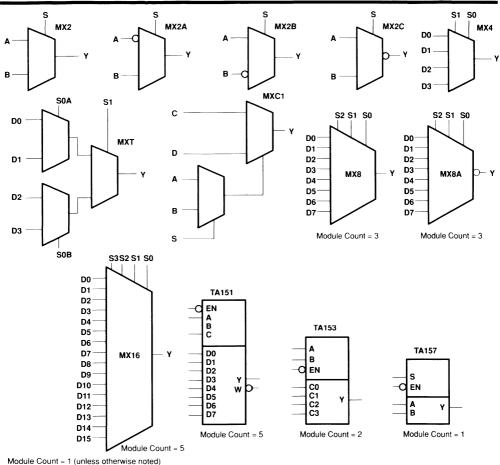

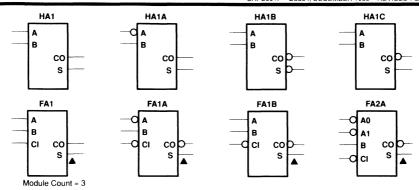

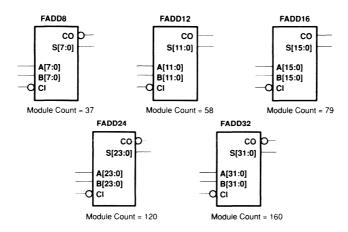

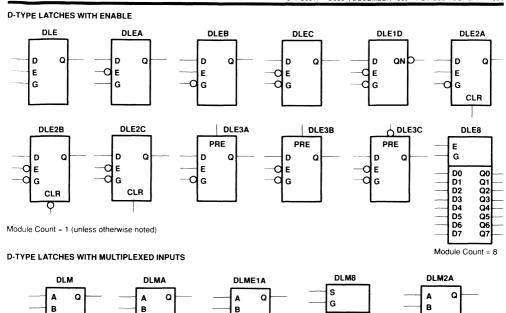

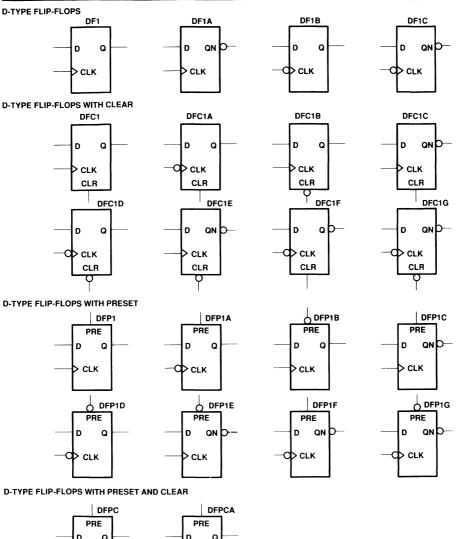

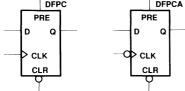

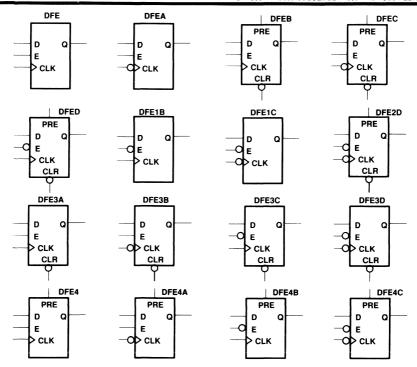

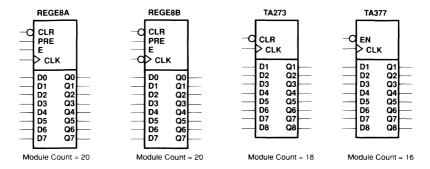

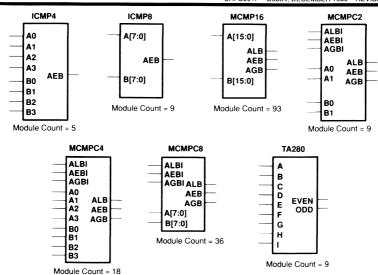

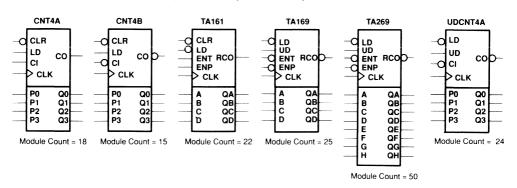

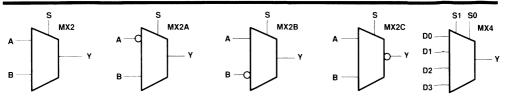

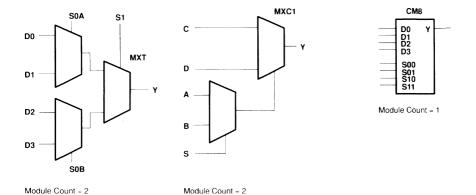

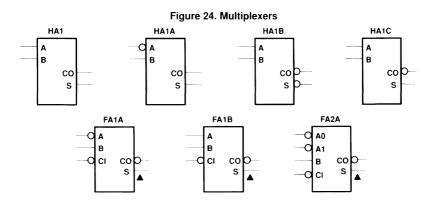

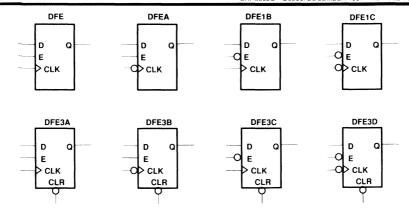

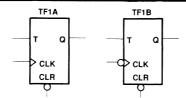

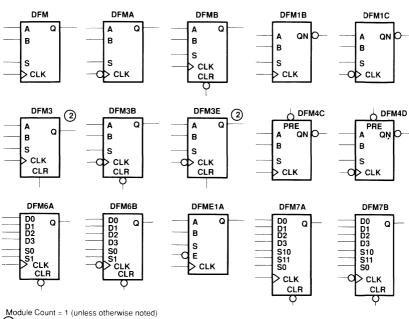

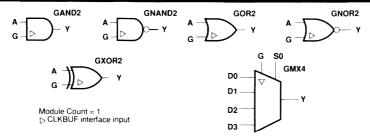

The TPC10 Series FPGA library contains over 250 logic building blocks of hardwired and soft macros. The hardwired macros provide a wide selection of predesigned, fully characterized functions. The soft macros provide popular MSI functions that can be called into the design. Additional user-defined soft macros can be created using the TPC10 library macros. The library contains the following classes of macros:

- Primitive Gates, Booleans, and Buffers

- CMOS, TTL, and Clock Buffer Inputs and Totem-Pole, 3-State, and I/O Output Buffers

- Adders and Multiplexers

- D-Type Flip-Flops

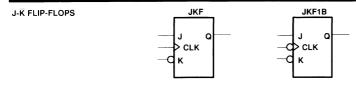

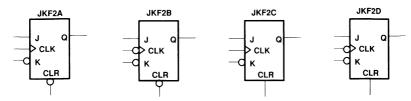

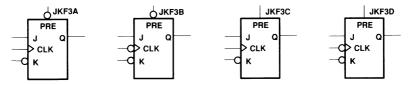

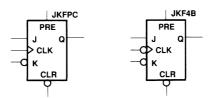

- J-K Flip-Flops

- Latches

- MSI Complexity Soft Macros

# design flow

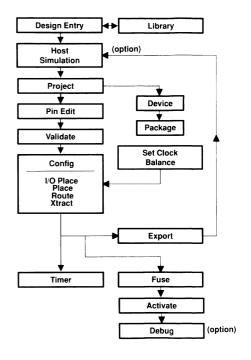

Custom logic functions, designed in conjunction with the TPC10 Series FPGA library, can be simulated and verified prior to creating the ALS design data base and programming files. Figure 1 provides an overview of the design flow.

Figure 1. Design Flow

# TPC10 SERIES CMOS FIELD-PROGRAMMABLE GATE ARRAYS

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

| Table 2. TI-ALS Design Configurations (see Note 1 | Table | 2. | TI-ALS | Design | Configurations | (see Note 1 | ١ |

|---------------------------------------------------|-------|----|--------|--------|----------------|-------------|---|

|---------------------------------------------------|-------|----|--------|--------|----------------|-------------|---|

| HARDWARE         | LIBRARY/CAE HOST  | DESIGN SUPPORT (gates) |             | TI SUSTEM         |  |

|------------------|-------------------|------------------------|-------------|-------------------|--|

| PLATFORM         | ENVIRONMENT       | UP TO 2500             | UP TO 10000 | PART NUMBER       |  |

|                  | View <i>Logic</i> | Х                      |             | TPC-ALS-DSPC-VL   |  |

| 386/486-based    | View <i>Logic</i> |                        | X           | TPC-ALS-DA-PC-VL  |  |

| PC               | OrCAD             | X                      |             | TPC-ALS-DS-PC-OR  |  |

|                  | OrCAD             |                        | X           | TPC-ALS-DA-PC-OR  |  |

|                  | Cadence           |                        | X           | TPC-ALS-DA-SN-CD  |  |

| Sun              | Mentor            |                        | X           | TPC-ALS-DA-SN-MG  |  |

| Suii             | Valid             |                        | Х           | TPC-ALS-245†      |  |

|                  | View <i>Logic</i> |                        | X           | TPC-ALS-DA-SN-VL  |  |

| HP700            |                   |                        |             | TPC-ALS-DA-HP7-MG |  |

| DN4000/<br>HP400 | Mentor            |                        | Х           | TPC-ALS-235†      |  |

NOTE 1: Authorization codes for design systems are supplied upon request, after receipt of the system.

Table 3. TI-ALS Programming Configurations (see Note 2)

| HARDWARE      | CAE HOST          | DESIGN                  | SUPPORT | TI SUSTEM          |  |

|---------------|-------------------|-------------------------|---------|--------------------|--|

| PLATFORM      | ENVIRONMENT       | ONE DEVICE FOUR DEVICES |         | PART NUMBER        |  |

| 386/486-based | View Lee's (O-CAD | Х                       |         | TPC-ALS-DS-P2S-PC  |  |

| PC            | ViewLogic /OrCAD  |                         | Х       | TPC-ALS-219        |  |

| Sun           | Cadence/Mentor/   | X                       |         | TPC-ALS-DSP2S-SN   |  |

|               | Valid/ViewLogic   |                         | X       | TPC-ALS-249        |  |

| HP700         | Mentor            | X                       |         | TPC-ALS-DS-P2S-HP7 |  |

|               | Mentor            |                         | х       | TPC-ALS-DS-P2-HP7  |  |

| 110400        | Mentor            | X                       |         | TPC-ALS-DS-P2S-HP4 |  |

| HP400         | Mentor            |                         | х       | TPC-ALS-DS-P2-HP4  |  |

| DN Series     | Mentor            |                         | Х       | TPC-ALS-239        |  |

NOTE 2: Programming units are compatible with both high (10000 gates) and low (2500 gates) density systems.

<sup>†</sup> The TPC-ALS-235 and TPC-ALS-245 systems only provide support for the TPC10 and TPC12 series, and will not be supported in Revision 3.0 scheduled for release in the fourth quarter of 1993. These systems are being replaced by TPC-ALS-DA-HP7-MG and TPC-ALS-DA-SN-CD, respectively.

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

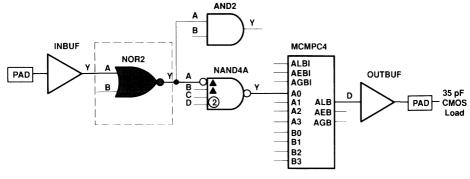

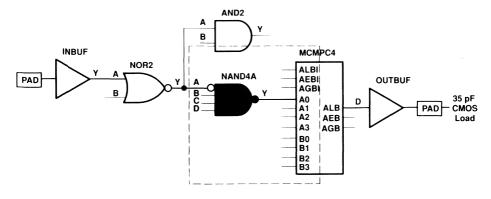

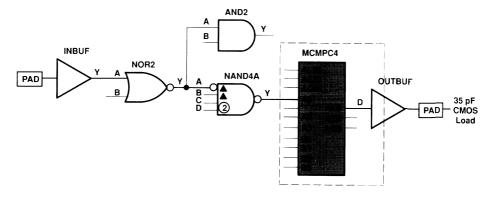

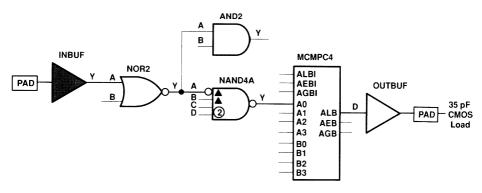

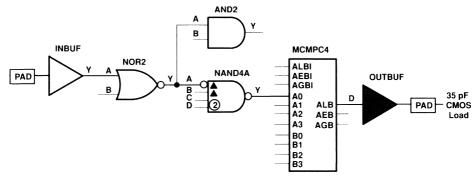

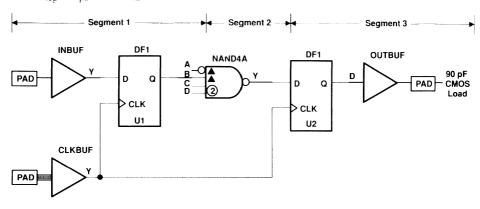

#### architecture

# device organization

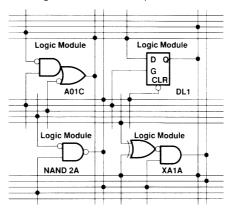

Each FPGA consists of a matrix of logic modules arranged in rows separated by channels containing interconnect tracks. The matrix is surrounded with peripheral inputs, outputs, I/Os, and diagnostic circuits. A partial view of the TPC10 Series logic modules with examples of interconnections is illustrated in Figure 2.

Figure 2. Partial View of TPC10 Series Interconnection Capability

# logic module

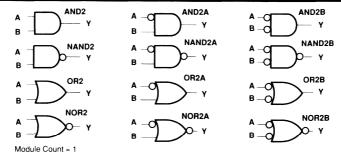

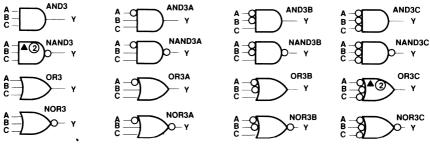

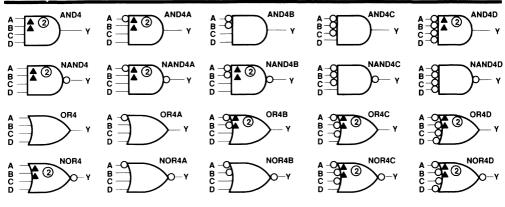

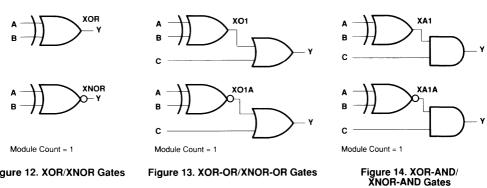

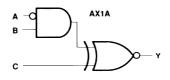

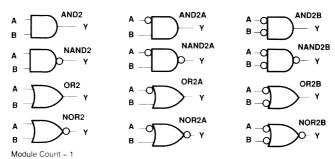

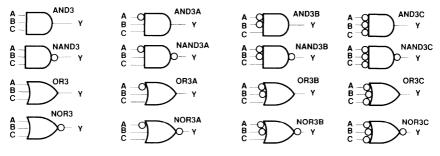

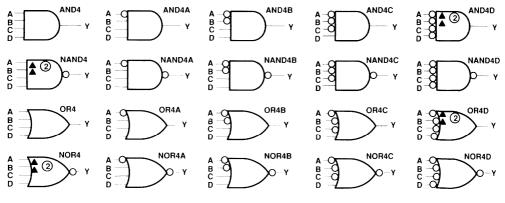

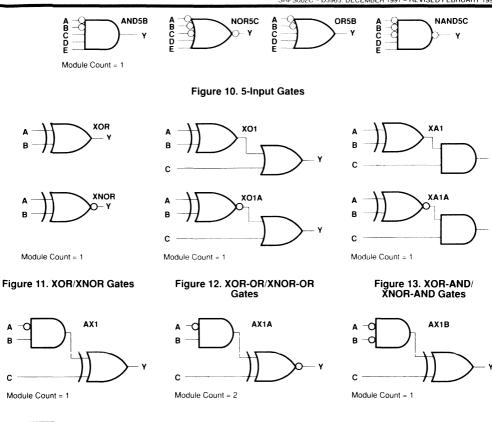

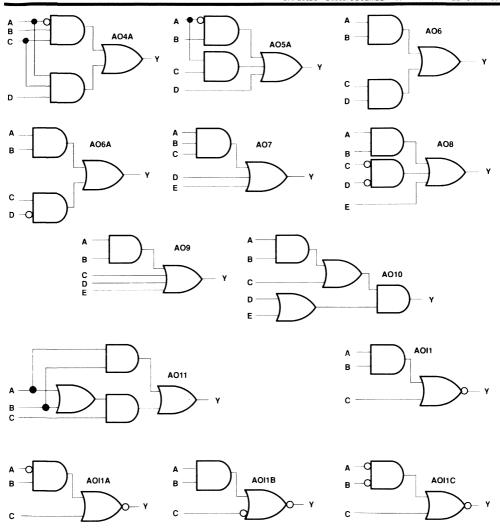

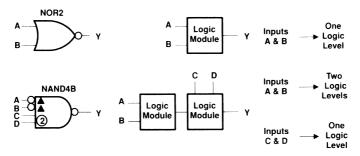

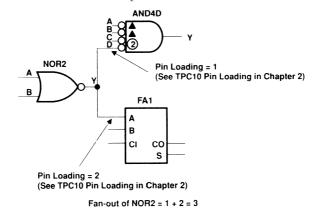

Each core logic module has the equivalent complexity of four 2-input NAND gates. The module shown in Figure 3, is an 8-input, 1-output gate cluster that can implement hardwired primitive gates, Booleans, latches, flip-flops, multiplexers, half or full adder slices, or multiplexed-input flip-flops. The TI-ALS library contains a full spectrum of 2-, 3-, and 4-input AND, NAND, OR, and NOR gate macros covering all derivatives of true and/or complement input combinations. Similar modular implementations, covering the spectrum of true and/or complement input combinations, are included for each functional category of macros in the library. Latches and flip-flops are created by connecting two or more logic modules in the appropriate circuit configuration. The macros are captured, simulated, placed, analyzed, and programmed using the TPC10 design library.

Figure 3. TPC10 Series Logic Module

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

#### interconnect tracks

The channeled interconnect tracks consist of isolated metal segments that can be connected by addressing and programming antifuses. Each channel has 25 horizontal routing tracks, 22 are for logic, one is for clock, one is for power, and one is for ground. In addition, there are 13 vertical routing tracks per logic module column. Both horizontal and vertical tracks, in combination with the approximately 340 antifuses per logic module, produce a network that is capable of interconnecting up to 90 percent of the equivalent gates. Based on the placement of macros, the programming process selects and activates antifuses that both create the logic module macros and I/Os, and interconnect the entire array.

#### I/O buffers

Each I/O pin is configurable as an input or an output. In addition, I/O pins configured as outputs can be defined as totem-pole, 3-state, or bidirectional. Inputs can be driven by CMOS or TTL levels and output levels are compatible with standard CMOS and TTL specifications. Outputs sink or source a current of 4 mA at TTL output levels. See the dc characteristics for additional I/O buffer specifications. The I/Os can be manually assigned to any available package pin, or the ALS software can automatically place the I/Os in the optimum configuration.

# diagnostic probe pins

TPC10 Series devices have two independent diagnostic probe pins, PRA and PRB. The pins allow the user to observe any internal signals by entering the appropriate net name in the diagnostic software. Signals may be viewed on an oscilloscope, logic analyzer, or with the workstation diagnostics using the Actionprobe diagnostic tools. The probe pins can also be used as user-defined I/Os, depending on the level of the mode control pin. When configured as user-defined I/Os, the pins have the same characteristics as other I/O pins.

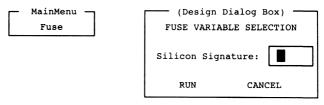

# security fuses

The TPC10 Series security fuses can be used to permanently disable further diagnostics and testing. After the security fuses are programmed, access to the architecture is not available. This makes the FPGA design difficult to copy.

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

# FPGA array performance

# logic module size

A mask-programmed gate array cell with four transistors usually implements only one logic level. The TPC10 Series array logic module is more complex and typically implements multiple logic levels within a single module. This reduces intermodule wiring and associated RC delays. In effect, the TPC10 logic module implements the equivalent of a net compression that enhances performance.

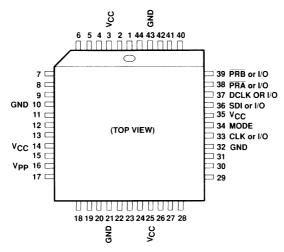

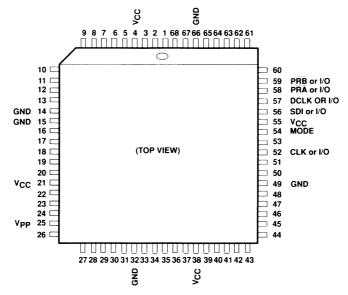

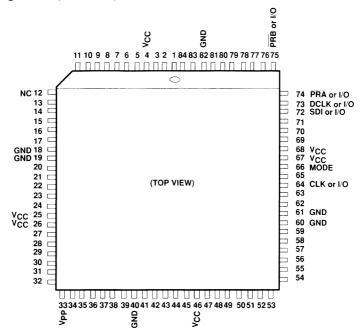

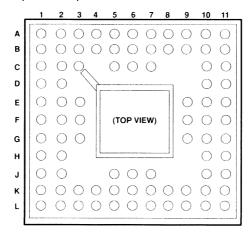

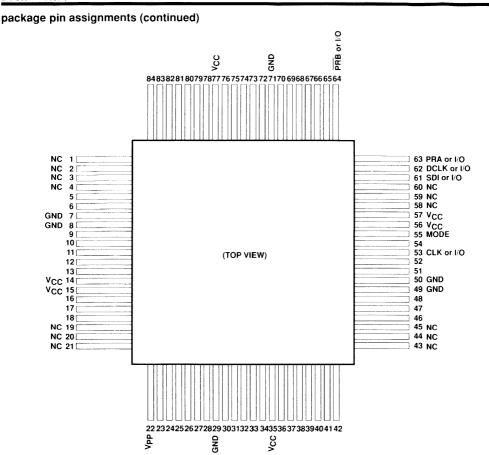

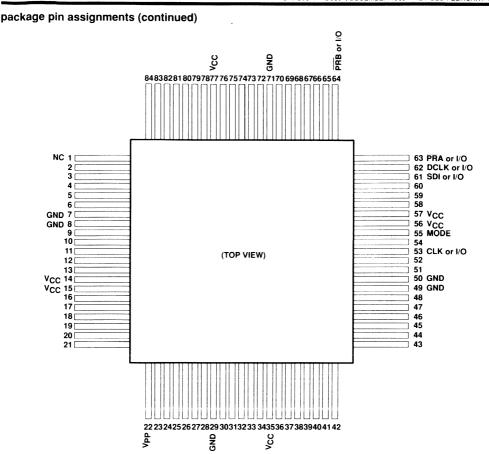

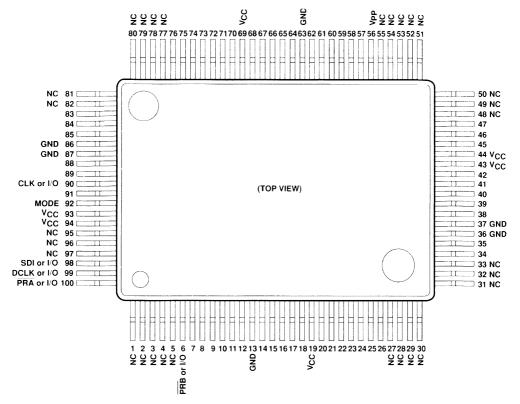

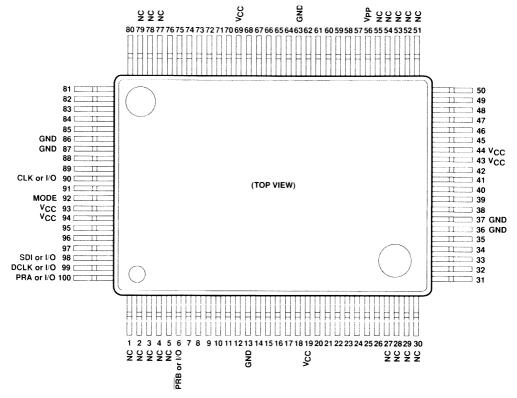

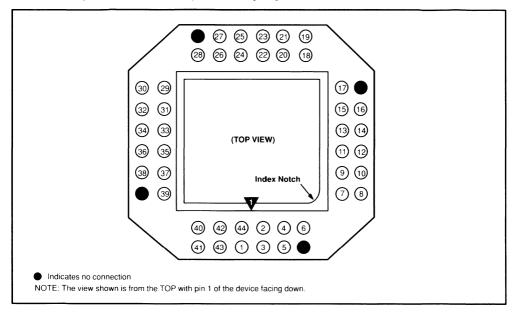

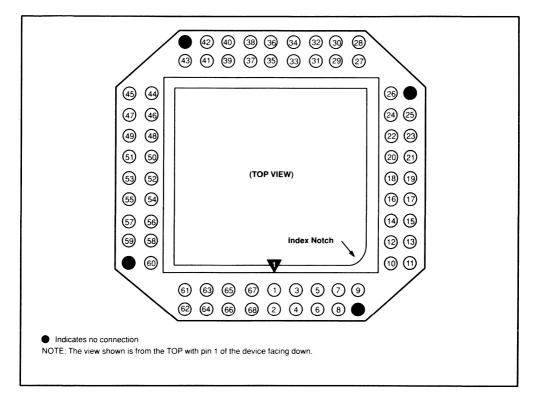

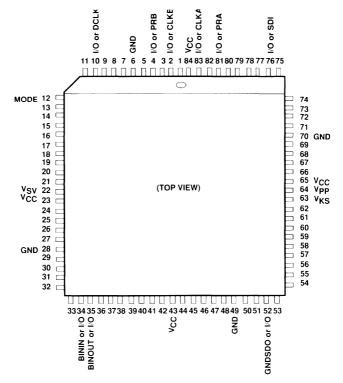

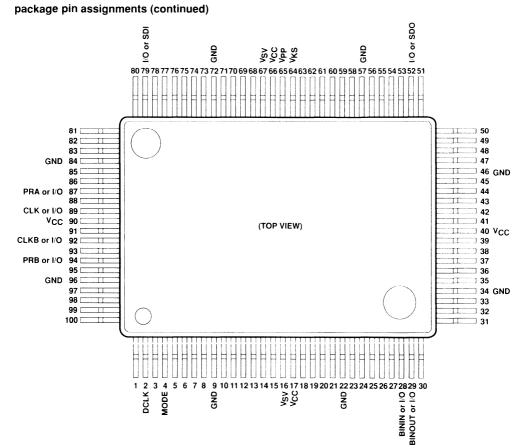

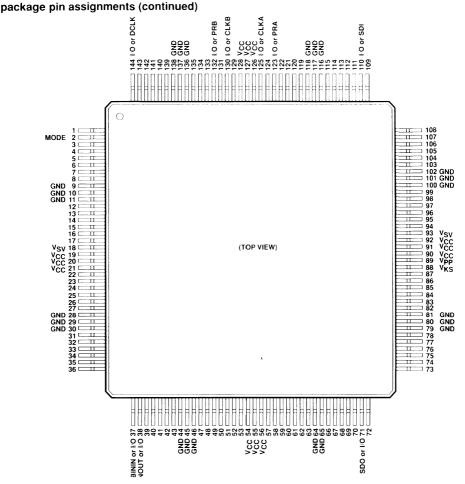

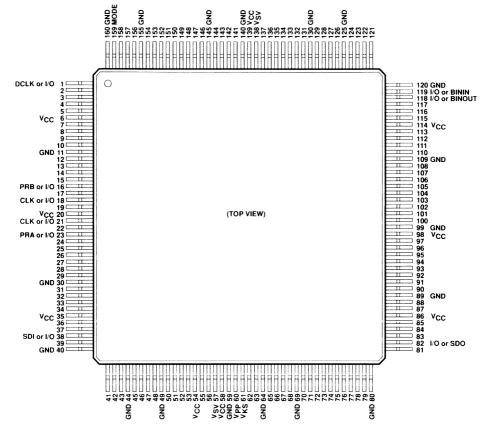

# **TERMINAL FUNCTIONS**

| PIN<br>NAME | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK         | 1   | Clock. TTL clock input for global clock distribution network. The clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.                                                                                                                                                                                                                                                                                                                                                                                           |

| DCLK        | 1   | Diagnostic clock. TTL clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is high. This pin functions as an I/O when the MODE pin is low.                                                                                                                                                                                                                                                                                                                                                                               |

| GND         | 1   | Ground. Input low supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I/O         | I/O | Input/output. I/O pin functions as an input, output. 3-state, or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/O pins are automatically set low by the ALS software.                                                                                                                                                                                                                                                                                                                       |

| MODE        | 1   | Mode. The MODE pin controls the use of multifunction pins (DCLK, PRA, PRB, SDI). When the MODE pin is high, the special functions are active. When the MODE pin is low, the pins function as I/Os.                                                                                                                                                                                                                                                                                                                                                            |

| NC          |     | No connection. This pin is not connected to circuitry within the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PRA         | 0   | Probe A. The probe A pin is used to output data from any user-defined design node within the device. This independent diagnostic pin is used in conjunction with the probe B pin to allow real-time diagnostic output of any signal path within the device. The probe A pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect the programmed design's confidentiality. PRA is active when the MODE pin is high. This pin functions as an I/O when the MODE pin is low. |

| PRB         | 0   | Probe B. The probe B pin is used to output data from any user-defined design node within the device. This independent diagnostic pin is used in conjunction with the probe A pin to allow real-time diagnostic output of any signal path within the device. The probe B pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect the programmed design's confidentiality. PRB is active when the MODE pin is high. This pin functions as an I/O when the MODE pin is low. |

| SDI         | ı   | Serial data input. Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is high. This pin functions as an I/O when the MODE pin is low.                                                                                                                                                                                                                                                                                                                                                                             |

| VCC         | 1   | Supply voltage. Input high supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VPP         | 1   | Programming voltage. Input supply voltage used for device programming. This pin must be connected to V <sub>CC</sub> during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                 |

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

|                                                                             | ,                              |

|-----------------------------------------------------------------------------|--------------------------------|

| Supply voltage range , V <sub>CC</sub>                                      | – 0.5 V to 7 V                 |

| Input voltage range, V <sub>1</sub>                                         |                                |

| Output voltage range, VO                                                    | 0.5 to V <sub>CC</sub> + 0.5 V |

| Input clamp current <sup>‡</sup> , $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ ) |                                |

| Output clamp current $V_O < 0$ or $V_O > V_{CC}$                            | ± 20 mA                        |

| Continuous output current§, $(V_O = 0 \text{ to } V_{CC})$                  | ± 25 mA                        |

| Operating free-air temperature range, TA: Commercial                        | 0°C to 70°C                    |

| Industrial                                                                  | 40°C to 85°C                   |

| Operating case temperature range, T <sub>C</sub> : Military                 | 55°C to 125°C                  |

| Storage temperature range                                                   |                                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# recommended operating conditions

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | MIN  | NOM | MAX                  | UNIT |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----|----------------------|------|

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Commercial | 4.75 | 5   | 5.25                 |      |

| $v_{CC}$        | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Industrial | 4.5  | 5   | 5.5                  | ٧    |

|                 | No. 200 per significant de la companya de la compan | Military   | 4.5  | 5   | 5.5                  |      |

| VPP             | Program pin voltage (while not programming)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Vcc        |      | VCC | ٧                    |      |

| ٧ <sub>IH</sub> | High-level input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | 2    |     | V <sub>CC</sub> +0.3 | ٧    |

| VIL             | Low-level input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | -0.3 |     | 0.8                  | ٧    |

| <del>-</del>    | O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Commercial | 0    | 25  | 70                   | °C   |